2

2

2

4

2

2

1

3

## INSTRUCTIONS

- 1. Printed, photocopied, phone, calculator etc. and exchange of any material is NOT allowed.

- 2. Solve questions serially in the answer script.

- 1. (a) Consider the 32 bit Hexadecimal number 0xcafe2b3a.

- 1. What is the binary representation of a number in little-endian format? Mark the bytes and number them from low (0) to high (3) bytes.

- 2. What is the binary representation of a number in big-endian format? Mark the bytes and number them from low (0) to high (3) bytes.

- (b) Suppose 32-bit instruction using the following format:

- If there are 250 opcodes and 125 registers

- 1. Determine the minimum number of bits required to represent the opcode.

- 2. What is the minimum number of bits required to represent the Source register (SR1 or SR2).

- 3. What is the minimum number of bits Unused in the instruction encoding?

- (c) 1. Compute 3-5 using 4-bit two's complement numbers.

- 2. Define a combinational circuit.

- 2. (a) Design an ALU that takes as input two N bit strings A, B and outputs the result of the following operation according to the value of additional input F. Please highlight how values of F affect the circuit. For smaller circuits like AND, OR, ADDITION you can use their schematic presentation.

| F         | 0       | 1      | 2     | 3        | 4                    | 5                   | 6     | 7   |

|-----------|---------|--------|-------|----------|----------------------|---------------------|-------|-----|

| Operation | A AND B | A OR B | A + B | not used | A AND $\overline{B}$ | A OR $\overline{B}$ | A - B | SLT |

- (b) What is the delay for (i) a ripple-carry adder and (ii) a carry-lookahead adder with 4-bit blocks of 64-bit adders? Assume that each two-input gate delay is 150 ps and that a full adder delay is 450 ps.

- 3. (a) Define a finite state machine and draw state diagram for the danger sign controller. Assume that the danger sign has five LEDs making an arrow sign that suggests to 'move right'.

- (b) Design a sequential logic circuit for the danger sign controller and draw its outline using two CLUs and two storage elements.

- (c) Draw gate-level description of the two CLUs used.

- 4. Simplify the following Boolean equations using Boolean theorems. Show your steps and verify it using K-maps.

(a)

$$Y = AC + \bar{A}\bar{B}C$$

$1~{\rm of}~2$

1

- (b)  $Y = \overline{A}\overline{B} + \overline{A}C\overline{B} + (\overline{A} + \overline{C})$ (c)  $Y = \overline{A}\overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C} + A\overline{B}C\overline{D} + ABD + \overline{A}\overline{B}C\overline{D} + B\overline{C}D + \overline{A}$

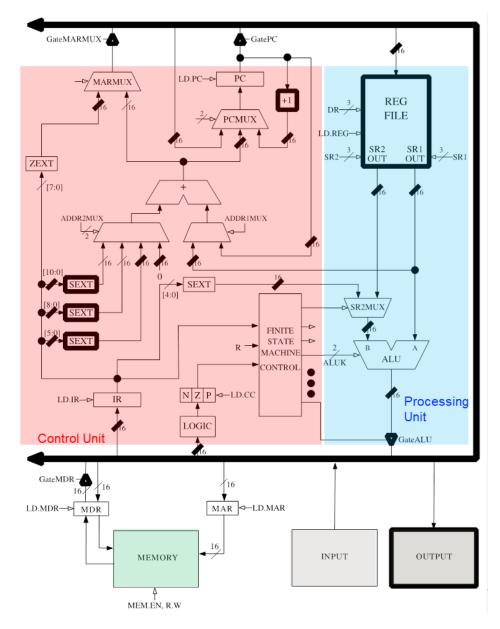

- 5. (a) Given the data path of LC-3 in Figure 1, with a semantic of Store ADD instruction as outlined below, list the correct sequence of every control signal set by the FSM to implement the instruction processing cycle. The instruction processing cycle includes Fetch, Decode, Evaluate Address, Fetch Operand, Execute, and Store Results. ADD RO, R1, R2 // RO=R1+R2

2

3

6

Figure 1: ISA Section Figure